Nabil Abdennadher Fabrice Kordon (Eds.)

# Reliable Software Technologies – Ada-Europe 2007

12th Ada-Europe International Conference on Reliable Software Technologies Geneva, Switzerland, June 2007, Proceedings

# Lecture Notes in Computer Science

4498

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

# Reliable Software Technologies – Ada-Europe 2007

12th Ada-Europe International Conference on Reliable Software Technologies Geneva, Switzerland, June 25-29, 2007 Proceedings

#### Volume Editors

Nabil Abdennadher University of Applied Sciences Western Switzerland, HES.SO École d'ingénieurs de Genève Rue de la Prairie 4, 1202 Geneva, Switzerland E-mail: Nabil.Abdennadher@hesge.ch

Fabrice Kordon Université Pierre et Marie Curie Laboratoire d'Informatique de Paris 6 104 Avenue du Président Kennedy, 75016 Paris, France E-mail: Fabrice.Kordon@lip6.fr

Library of Congress Control Number: 2007929319

CR Subject Classification (1998): D.2, D.1.2-5, D.3, C.2.4, C.3, K.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-73229-2 Springer Berlin Heidelberg New York ISBN-13 978-3-540-73229-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12080861 06/3180 5 4 3 2 1 0

# **Preface**

Reliable Software Technologies is an annual series of international conferences devoted to the promotion and advancement of all aspects of reliable software technologies. The objective of this series of conferences, initiated and sponsored by Ada-Europe, the European federation of national Ada societies, is to provide a forum to promote the development of reliable softwares both as an industrial technique and an academic discipline.

Previous editions of the Reliable Software Technologies conference were held in: Porto (Portugal) in 2006, York (UK) in 2005, Palma de Mallorca (Spain) in 2004, Toulouse (France) in 2003, Vienna (Austria) in 2002, Leuven (Belgium) in 2001, Potsdam (Germany) in 2000, Santander (Spain) in 1999, Uppsala (Sweden) in 1998, London (UK) in 1997 and Montreux (Switzerland) in 1996.

The 12th International Conference on Reliable Software Technologies took place in Geneva, Switzerland, June 25-29, 2007, under the continued sponsoring of Ada-Europe, in cooperation with ACM SIGAda. It was organized by members of the University of Applied Sciences, Western Switzerland (Engineering School of Geneva), in collaboration with colleagues from various places in Europe. The 13th conference, in 2008, will take place in Venice, Italy.

Continuing the success achieved in previous years, the conference included a three-day technical program, where the papers contained in these proceedings were presented. The technical program was bracketed by two tutorial days where attendants had the opportunity to catch up on a variety of topics related to the fields covered by the conference, at both introductory and advanced levels. The technical program also included an industrial track, with contributions illustrating challenges faced and solutions devised by industry from both sides of the Atlantic, as well as from the rest of the world (we note several contributions from South-East Asia). Furthermore, the conference was accompanied by an exhibition where vendors presented their products for supporting the development of reliable software.

The conference featured four distinguished speakers, who delivered state-ofthe-art information on topics of great importance, both for the present and the future of software engineering:

Challenges for Reliable Software Design in Automotive Electronic Control Units

Synchronous Techniques for Embedded Systems

Perspectives on Next-Generation Software Engineering

Observation Rooms for Program Execution Monitoring

We would like to express our sincere gratitude to these distinguished speakers for sharing their insights with the conference participants.

A large number of regular papers were submitted, from as many as 15 different countries. The Program Committee worked hard to review them, and the selection process proved to be difficult, since many papers had received excellent reviews. The Program Committee eventually selected 18 papers for the conference and these proceedings.

The industrial track of the conference also received valuable contributions from industry, and the Industrial Committee selected nine of them for presentation in Geneva. The final result was a truly international program with contributions from Australia, Austria, China, France, Germany, Italy, Republic of Korea, Spain, Tunisia, and the UK, covering a broad range of topics: real-time systems, static analysis, verification, applications, reliability, industrial experience, compilers and distributed systems.

The conference also included an interesting selection of tutorials, featuring international experts who presented introductory and advanced material in the domain of the conference:

- An Overview of Model-Driven Engineering,

- CbyC: A UML2 Profile Enforcing the Ravsenscar Computational Model,

- Object-Oriented Programming in Ada 2005, ...

- Security by Construction,

- Synchronous Design of Embedded Systems: the Esterel/Scade Approach,

- Building Interoperable Applications with PolyORB, .......

- Situational Method Engineering: Towards a Specific Method for Each System Development Project,

We wish to extend our gratitude to these experts for the work they put into preparing and presenting this material during the conference.

The 12th Reliable Software Technologies (Ada-Europe 2007) conference was made possible through the generous support and diligent work of many individuals and organizations. A number of institutional and industrial sponsors also made important contributions and participated in the industrial exhibition. Their names and logos appear on the Ada-Europe 2007 Web site. We gratefully acknowledge their support. A subcommittee comprising Nabil Abdennadher, Dirk Craeynest, Fabrice Kordon, Dominik Madon, Ahlan Marriott, Tullio Vardanega and Luigi Zaffalon met in Geneva to elaborate the final program selection. Various Program Committee members were assigned to shepherd some of the papers. We are grateful to all those who contributed to the technical program of the conference.

We would like to thank the members of the Organizing Committee for their valuable effort in taking care of all the details needed for a smooth run of the

conference. Dominik Madon did a superb job in organizing an attractive tutorial program. Luigi Zaffalon took on the difficult task of preparing the industrial track. We would also like to thank Dirk Craeynest and Ahlan Marriott, who worked very hard to make the conference prominently visible, and to all the members of the Ada-Europe board for helping with the intricate details of the organization. Special thanks go to Régis Boesch and Albena Basset, who took care of all details of the local organization.

Finally, we also thank the authors of the contributions submitted to the conference, and to all the participants who helped in achieving the goal of the conference: to provide a forum for researchers and practitioners for the exchange of information and ideas about reliable software technologies. We hope they all enjoyed the program as well as the social events of the 12th International Conference on Reliable Software Technologies.

June 2007

Nabil Abdennadher Fabrice Kordon

# Organization

### Conference Chair

Nabil Abdennadher, University of Applied Sciences, Geneva, Switzerland

# **Program Co-chairs**

Nabil Abdennadher, University of Applied Sciences, Geneva, Switzerland Fabrice Kordon, Université Pierre & Marie Curie, Paris, France

## **Industrial Committee Chair**

Luigi Zaffalon, University of Applied Sciences, Geneva, Switzerland

## **Tutorial Chair**

Dominik Madon, University of Applied Sciences, Geneva, Switzerland

### **Exhibition Chair**

Neville Rowden, Siemens Switzerland

# **Publicity Co-chairs**

Ahlan Marriott, White-elephant, Switzerland Dirk Craeynest, Aubay Belgium and K.U.Leuven, Belgium

#### Local Chair

Régis Boesch, University of Applied Sciences, Geneva, Switzerland

# Ada-Europe Conference Liaison

Fabrice Kordon, Université Pierre et Marie Curie, Paris, France

# Program Committee

Abdennadher Nabil, University of Applied Sciences, Geneva, Switzerland Alonso Alejandro, Universidad Politécnica de Madrid, Spain Asplund Lars, Mälardalens Högskola, Sweden Barnes Janet, Praxis High Integrity Systems, UK

#### Organization

Χ

Blieberger Johann, Technische Universität Wien, Austria Boasson Maartin, University of Amsterdam, The Netherlands Burgstaller Bernd, University of Sydney, Australia Craeynest Dirk, Aubay Belgium and K.U.Leuven, Belgium Crespo Alfons, Universidad Politécnica de Valencia, Spain Devillers Raymond, Université Libre de Bruxelles, Belgium González Harbour Michael, Universidad de Cantabria, Spain

Gutiérrez José Javier, Universidad de Cantabria, Spain

Hadded Serge, Université Paris-Dauphine, France

Hately Andrew, Eurocontrol CRDS, Hungary

Hommel Günter, Technische Universität Berlin, Germany

Keller Hubert, Institut für Angewandte Informatik, Germany

Kermarrec Yvon, ENST Bretagne, France

Kienzle Jörg, McGill University, Canada

Kordon Fabrice, Université Pierre et Marie Curie, France

Llamosi Albert, Universitat de les Illes Balears, Spain

Lundqvist Kristina, MIT, USA

Mazzanti Franco, ISTI-CNR Pisa, Italy

McCormick John, University of Northern Iowa, USA

Michell Stephen, Maurya Software, Canada

Miranda Javier, Universidad Las Palmas de Gran Canaria, Spain

Moldt Daniel, University of Hamburg, Germany

Pautet Laurent, Telecom Paris, France

Petrucci Laure, LIPN, Université Paris 13, France

Pinho Luís Miguel, Polytechnic Institute of Porto, Portugal

Plödereder Erhard, Universität Stuttgart, Germany

de la Puente Juan A., Universidad Politécnica de Madrid, Spain

Real Jorge, Universidad Politécnica de Valencia, Spain

Romanovsky Alexander, University of Newcastle upon Tyne, UK

Rosen Jean-Pierre, Adalog, France

Ruiz José, AdaCore, France

Schonberg Edmond, New York University and AdaCore, USA

Seinturier Lionel, INRIA Lille, France

Shing Man-Tak, Naval Postgraduate School, USA

Tokar Joyce, Pyrrhus Software, USA

Vardanega Tullio, Università di Padova, Italy

Wellings Andy, University of York, UK

Winkler Jürgen, Friedrich-Schiller-Universität, Germany

Zaffalon Luigi, University of Applied Sciences, Geneva, Switzerland

# Sponsoring Institutions

Ada-Europe AdaCore Aonix Ellidiss Sowftare

Green Hills Software Inc.

Praxis

PostFinance Sun Microsystems Siemens Telelogic Fédération des Entreprises Romandes Swiss Informatics Society The Quality Software Foundation

# **Table of Contents**

| Real-Time Utilities for Ada 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Handling Temporal Faults in Ada 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15  |

| ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Implementation of New Ada 2005 Real-Time Services in MaRTE OS and GNAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29  |

| Enhancing Dependability of Component-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41  |

| Emilancing Dependability of Component-Based Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| On Detecting Double Literal Faults in Boolean Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55  |

| Static Detection of Livelocks in Ada Multitasking Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69  |

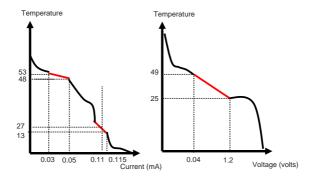

| Towards the Testing of Power-Aware Software Applications for Wireless Sensor Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84  |

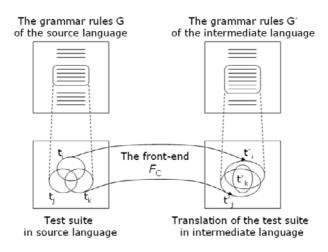

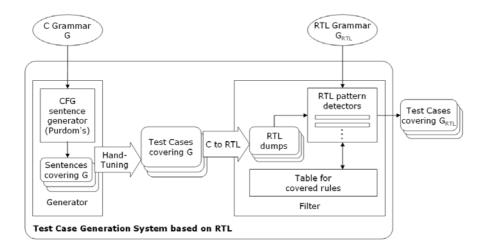

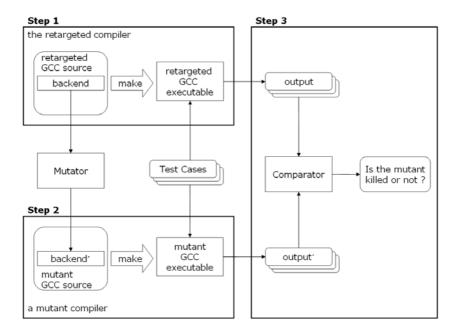

| An Intermediate Representation Approach to Reducing Test Suites for Retargeted Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 |

| the second of th |     |

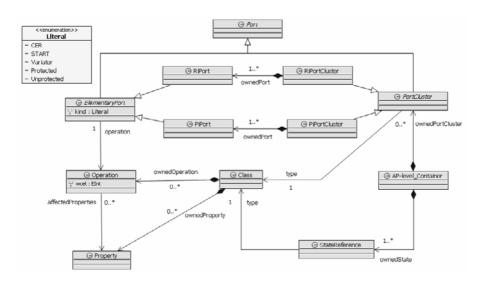

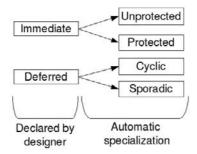

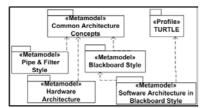

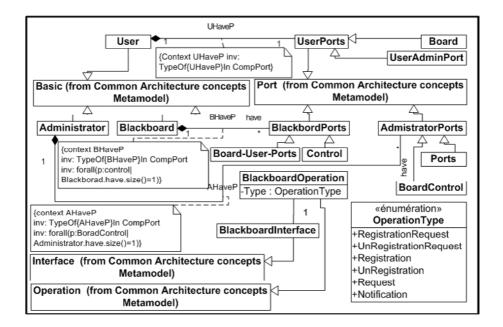

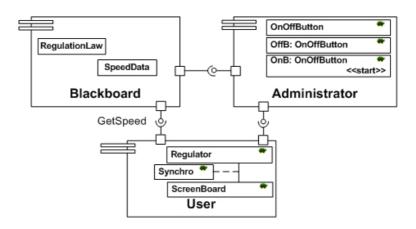

| Correctness by Construction for High-Integrity Real-Time Systems: A Metamodel-Driven Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

| A Metamodel-Driven Process Featuring Advanced Model-Based Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 128 |

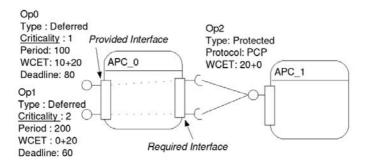

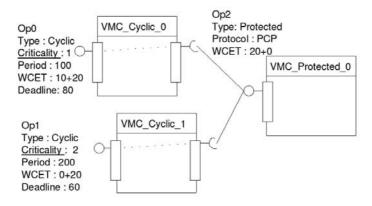

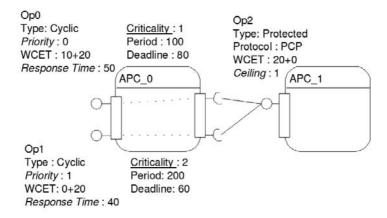

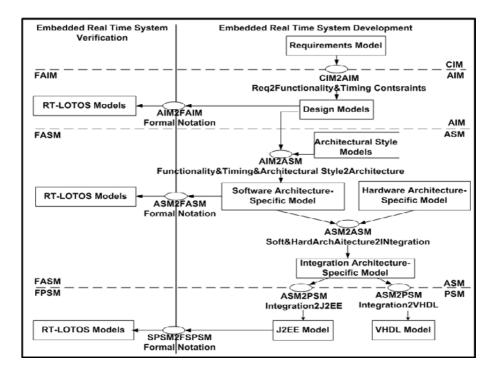

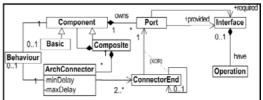

| ArchMDE Approach for the Development of Embedded Real Time Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 142 |

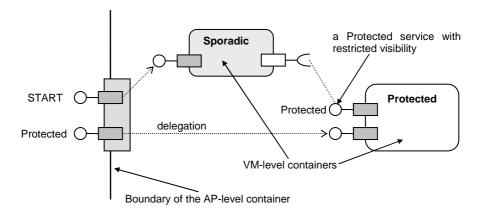

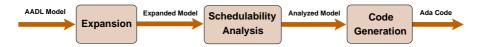

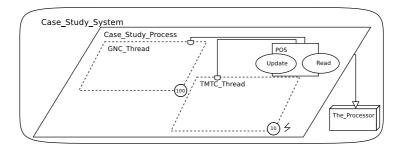

| Generating Distributed High Integrity Applications from Their Architectural Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 155 |

# XIV Table of Contents

| Automatic Ada Code Generation Using a Model-Driven Engineering Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 168 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| to the form of the second seco |     |

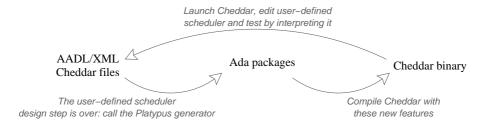

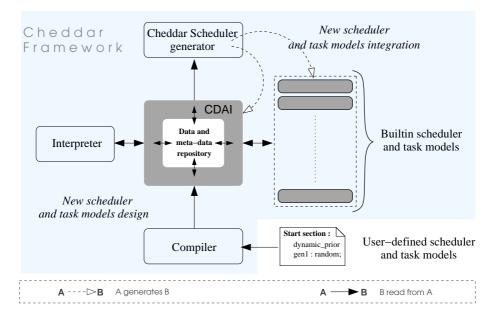

| Towards User-Level Extensibility of an Ada Library: An Experiment with Cheddar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 180 |

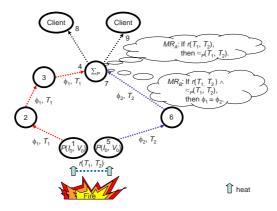

| Modelling Remote Concurrency with Ada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 192 |

| you con a postupe property and a second second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

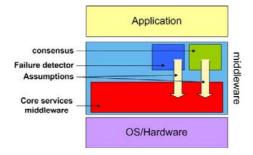

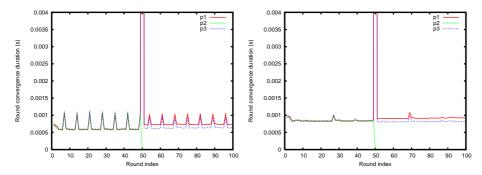

| Design and Performance of a Generic Consensus Component for Critical Distributed Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 208 |

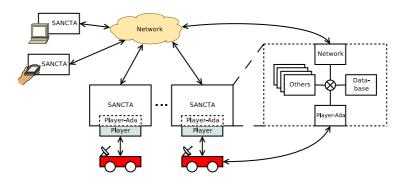

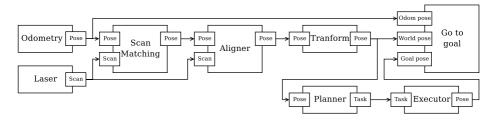

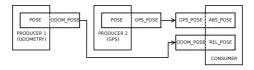

| SANCTA: An Ada 2005 General-Purpose Architecture for Mobile Robotics Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 221 |

| Incorporating Precise Garbage Collection in an Ada Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 235 |

| Author Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 247 |

# Real-Time Utilities for Ada 2005\*

Andy Wellings and Alan Burns

Department of Computer Science, University of York, UK {andy, burns}@cs.york.ac.uk

**Abstract.** Modern large real-time systems are becoming more complex. Whilst Ada 2005 provides a comprehensive set of programming mechanisms that allow these systems to be implemented, the abstractions are low level. This paper argues that there is a need for a standardised library of real-time utilities that address common real-time problems. The paper presents some initial considerations on what could be in such a library and how it could be structured.

### 1 Introduction

Ada has comprehensive support for priority-based real-time systems. The approach has been to provide a set of low-level mechanisms that enable the programmer to construct systems solving common real-time problems. Whilst eminently flexible, this approach requires the programmer to re-implement common paradigms in each new system. In the past, these structures have been quite straightforward, perhaps just involving simply periodic or sporadic tasks communicating via protected data. However, modern large real-time systems are much more complex and include hard, soft and non real-time components. The resulting paradigms are similarly more involved, and require activities like deadline miss detection, CPU budget overrun detection, the sharing of CPU budgets between aperiodic threads etc. Ada 2005 has responded admirably, expanding its set of low-level mechanisms. However, the common problems are now much more complex, and it is no longer appropriate to require the programmer to reconstruct the algorithms in each new system. Instead, what is required is a library of reusable real-time utilities; indeed, ideally such a library should become a de facto secondary standard – perhaps in the same way that Java has developed a set of concurrency utilities over the years that have now been incorporated into the Java 1.5 distribution.

The goal of this paper is to initiate a discussion in the Ada community to both confirm the need for a library of common real-time utilities and to propose (as a starting point) a framework for their construction.

#### 2 Real-Time Utilities – Framework Overview

In the field of real-time programming, real-time tasks are often classified as being periodic, sporadic or aperiodic. Simple real-time periodic tasks are easy to program but

<sup>\*</sup> This work has been undertaken within the context of the EU ARTIST2 project.

N. Abdennahder, F. Kordon (Eds.): Ada-Europe 2007, LNCS 4498, pp. 1–14, 2007.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2007

once more complicated ones are needed (such as those that detect deadline misses, execution time (budget) overruns, minimum inter-arrival violations etc), the paradigms become more complex. Hence, there is a need to package up some of these and provide them as real-time tasking utilities.

A programmer wanting to use a real-time tasking abstraction will want to indicate (for example):

- whether the abstraction is periodic, sporadic or aperiodic (each task is "released" in response to a release event, which is usually time triggered for periodic tasks and event triggered for sporadic and aperiodic tasks);

- whether to terminate the current release of the task in the event of a deadline miss

or to simply inform the program that this event has occurred (in which case, the

programmer can choose to react or ignore the event);

- whether to terminate the current release of the task in the event of an execution time overrun or to simply inform the program that this event has occurred (in which case, the program can choose to react or ignore the event);

- whether a task is associated with an execution-time server that can limit the amount of CPU-time it receives.

- whether a task can operate in one or more modes, and if so, the nature of the mode change.

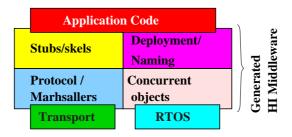

This paper illustrates how real-time task abstractions, supporting some of these variations, can be developed in Ada 2005. The approach that has been taken is to divide the support for the tasks into four components.

- 1. The functionality of the task this is encapsulated by the Real\_Time\_Task\_—State package. Its goal is to define a structure for the application code of the tasks. It is here that code is provided: to execute on each release of the task, to execute when deadline misses occur and when execution time overruns occurs. In this paper, it is assumed that the task only wishes to operate in a single mode.

- 2. The mechanisms needed to control the release of the real-time tasks and to detect the deadline misses and execution time overruns this is encapsulated in the Release\_Mechanisms package. Each mechanism is implemented using a combinations of protected objects and the new Ada 2005 timer and execution time control features.

- The various idioms of how the task should respond to deadline misses and execution time overruns – this is encapsulated in the Real\_Time\_Task package. It is here that the actual Ada tasks are provided.

- 4. The mechanisms needed to encapsulate subsystems and ensure that they are only given a fixed amount of the CPU resource (often called temporal firewalling) this is the responsibility of the Execution\_Servers package. This paper considers using these mechanisms to support aperiodic task execution only.

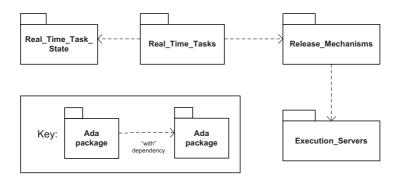

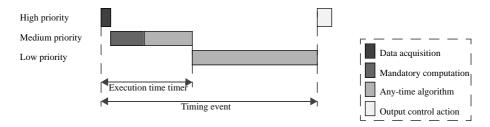

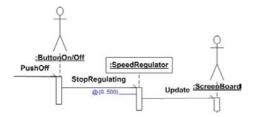

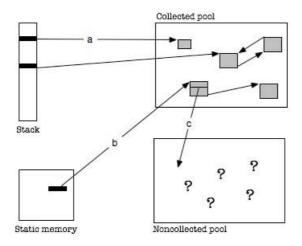

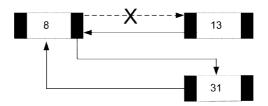

Figure 1 illustrates the top level packages that make up the abstractions. The details are discussed in the following sections.

Fig. 1. Top-Level Packages

# 3 Framework Design

This section describes the details of the design of the framework introduced in Section 2. It assumes fixed priority scheduling and that the deadlines of all periodic tasks are less than or equal to their associated periods.

#### 3.1 Real-Time Task State

First, it is necessary to provide a structure within which the programmer can express the code that the real-time task wishes to execute, along with its associated state variables. This is achieved, in the usual Ada object-oriented fashion, by defining the state within a tagged type, and providing operations to execute on the state. The following package shows the state and operations that all real-time tasks need.

```

-- with and use clauses omitted

package Real_Time_Task_State is

type Task_State is abstract tagged record

Relative_Deadline : Time_Span := Time_Span_Last;

Execution_Time : Time_Span := Time_Span_Last;

Pri : Priority := Default_Priority;

end record;

procedure Initialize(S: in out Task_State) is abstract;

procedure Code(S: in out Task_State) is abstract;

procedure Deadline_Miss(S: in out Task_State) is null;

procedure Overrun(S: in out Task_State) is null;

type Any_Task_State is access all Task_State'Class;

end Real_Time_Task_State;

```

Every real-time task has a deadline, an execution time and a priority. Here, these fields are made public, but they could have just as well been made private and procedures to 'get' and 'set' them provided. No additional assumptions have been made about the values of these attributes. The operations to be performed on a task's state are given by four procedures:

- Initialize: this is used to initialize the state when the real-time task is created;

- Code: this is the code that is executed on each release of the task;

- Deadline\_Miss: this is the code that is executed if a deadline is missed.

- Overrun: this is the code that is executed if an execution time overrun occurs.

Note, all real-time code must provide the Initialize and the Code procedures. There are default null actions on a missed deadline and on an execution time overrun.

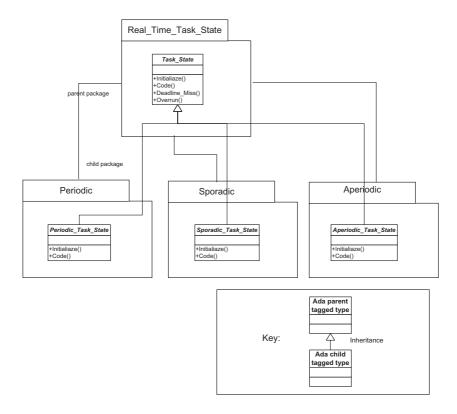

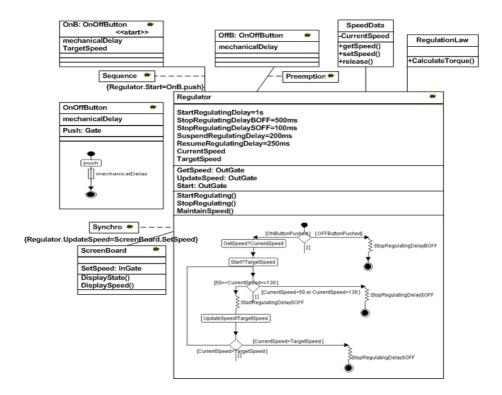

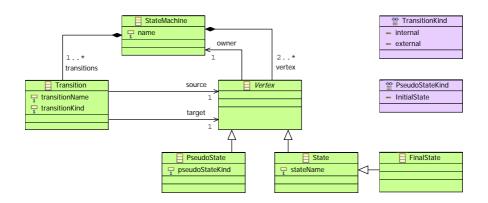

Child packages of Real\_Time\_Task\_State provide support for periodic, aperiodic and sporadic task execution (as illustrated in Figure 2).

Fig. 2. Task States

A periodic task's state includes that of a real-time task with the addition of its period of execution. In other words, it has regular time-triggered releases.

```

package Real_Time_Task_State.Periodic is

type Periodic_Task_State is abstract new Task_State with record

Period : Time_Span;

end record;

procedure Initialize(S: in out Periodic_Task_State) is abstract;

procedure Code(S: in out Periodic_Task_State)is abstract;

type Any_Periodic_Task_State is access all Periodic_Task_State'Class;

end Real Time Task State.Periodic;

```

There is more than one model of a sporadic task; here, it is assumed that the task must have an enforced minimum inter-arrival time between releases (another approach would be to enforce a maximum arrival frequency). Hence, the state includes this value.

```

package Real_Time_Task_State.Sporadic is

type Sporadic_Task_State is abstract new Task_State with record

MIT : Time_Span;

end record;

procedure Initialize(S: in out Sporadic_Task_State) is abstract;

procedure Code(S: in out Sporadic_Task_State) is abstract;

type Any_Sporadic_Task_State is access all Sporadic_Task_State'Class;

end Real_Time_Task_State.Sporadic;

```

The state for aperiodic tasks has no new fields over the normal Task\_State, but for uniformity, a new type can be created.

Application real-time tasks choose the appropriate real-time state to extend, and add their own state variables. For example, the following shows the application code to be used with the declaration of a periodic real-time task that is not interested in any missed deadlines or execution-time overruns.

```

type My_State is new Periodic_Task_State with record

-- state variables

end record;

procedure Initialize(S: in out My_State);

procedure Code(S: in out My_State);

Example_State: aliased My_State := (Pri=> System.Default_Priority + 1);

```

## 3.2 Real-Time Task Release Mechanisms

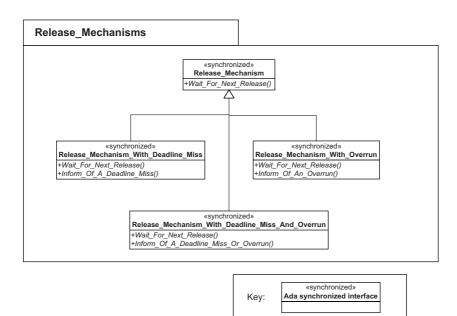

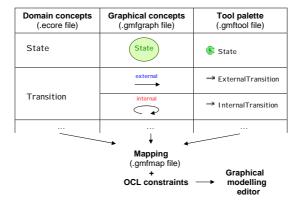

Real-time tasks can be released by the passage of time or via a software or hardware event. The following package (Release\_Mechanisms) provides the common interfaces for all mechanisms (illustrated in Figure 3).

The root of the interface hierarchy (Release\_Mechanism) simply supports the facility for a real-time task to wait for notification of its next release to occur (be that a time triggered or an event triggered release). The Release\_Mechanism\_With\_-Deadline\_Miss interface is provided for the case where the real-time task wishes to be informed when it has missed a deadline. Similarly, the Release\_Mechanism\_-With\_Overrun interface is provided for the case where the real-time task wishes to be informed when it has overrun it execution time. Finally, Release\_Mechanism\_-With\_Deadline\_Miss\_And\_Overrun allows both detection of deadline misses and execution time overruns. The Ada code is shown below for some of the above.

```

package Release_Mechanisms is

type Release_Mechanism is synchronized interface;

procedure Wait_For_Next_Release(R : in out Release_Mechanism) is abstract;

type Any_Release_Mechanism is access all Release_Mechanism'Class;

type Release_Mechanism_With_Deadline_Miss is

synchronized interface and Release_Mechanism;

procedure Wait_For_Next_Release(R : in out

Release_Mechanism_With_Deadline_Miss) is abstract;

procedure Inform_Of_A_Deadline_Miss(R : in out

Release_Mechanism_With_Deadline_Miss) is abstract;

```

Fig. 3. Release Mechanism Interfaces

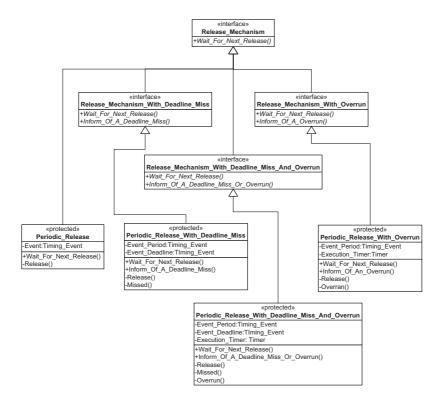

Child packages provide the actual release mechanisms – as illustrated in Figure 4 for periodic real-time tasks.

For example, the following shows the structure of a protected type that implements a periodic release mechanisms. The period of the task is obtained from the task's state, which is passed in as an access discriminant. The application code simply calls the Wait\_For\_Next\_Release entry.

```

-- with and use clauses omitted

package Release_Mechanisms.Periodic is

protected type Periodic_Release(S: Any_Periodic_Task_State) is

new Release_Mechanism with

entry Wait_For_Next_Release;

pragma Priority(System.Interrupt_Priority'Last);

private ...

end Periodic_Release;

end Release_Mechanisms.Periodic;

```

Another protected type can support deadline miss detection:

Fig. 4. Release Mechanism Classes

```

entry Inform_Of_A_Deadline_Miss;

pragma Priority(System.Interrupt_Priority'Last);

private ...

end Periodic_Release_With_Deadline_Miss;

end Release Mechanisms.Periodic And Deadline Miss Detection;

```

Here, a boolean indicates whether the application requires notification or termination of a deadline miss. If termination is required, the Inform\_Of\_A\_Deadline\_Miss entry can be used by the framework in a select-then-abort statement.

The implementation of these and the other release mechanism packages are discussed in Section 4.

## 3.3 Aperiodic Release Mechanisms and Execution servers

The final type of release mechanism is that for handling aperiodic releases. Typically, the CPU time allocated to aperiodic tasks must be constrained as they potentially can have unbounded resource requirements. The Ada 2005 group budget facility can be used to implement the various approaches.

Before the release mechanism can be programmed, it is necessary to consider how it interacts with the execution severs. This paper will only consider periodic execution servers. The following package specification defines the common interface.

```

type Server_Parameters is tagged record

Period : Time_Span;

Budget : Time_Span;

end record;

type Execution_Server is synchronized interface;

procedure Register(ES: in out Execution_Server; T : Task_Id) is abstract;

procedure Start_Session(ES: in out Execution_Server; T : Task_Id) is null;

procedure Complete_Session(ES: in out Execution_Server; T : Task_Id) is null;

type Any_Execution_Server is access all Execution_Server'Class;

end Execution_Servers;

```

All servers have parameters that determine the servers' characteristics. They include: the budget, how much CPU time has been allocated to the server, and the period (this relates to how often the server's budget is replenished). Two of the main servers found in the literature (the deferrable [2] and sporadic servers[5]) also require their clients to have foreground and background priorities, but in the general case this may not be the situation. Some servers suspend their clients when their execution time expires, and other servers allow their clients to have different priorities.